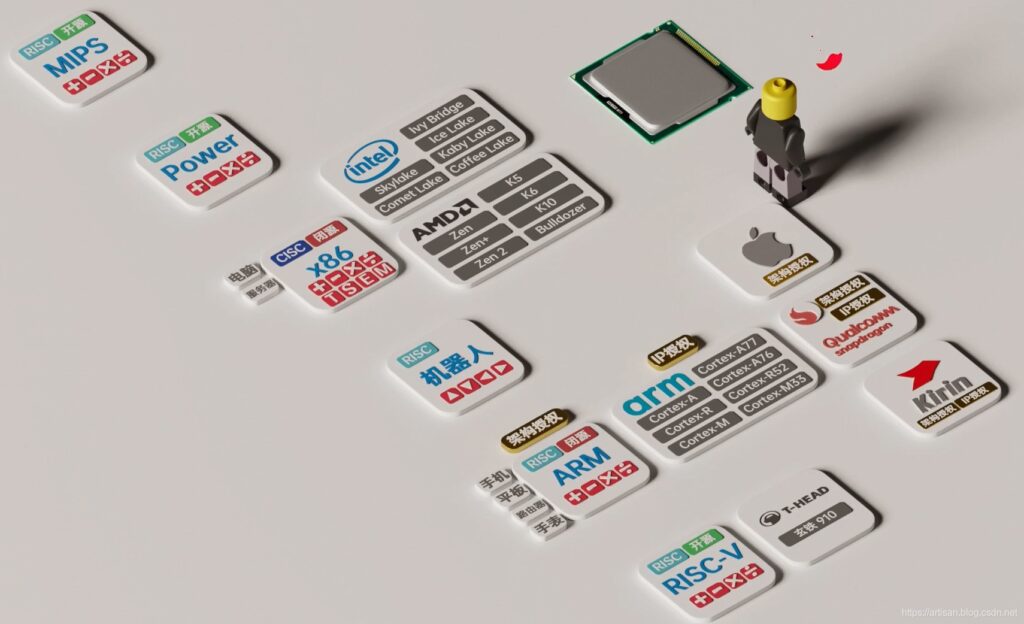

| ISA Type | ISA Name | Maker | First CPU |

| CISC | IBM System/360 | IBM | 1964 |

| CISC | Intel 8080 | Intel | 1974 |

| CISC | MOS 6502 | MOS Technology | 1975 |

| CISC | X86 | Intel, AMD | 1979 |

| CISC | m68k | Motorola | 1979 |

| RISC | Stanford MIPS | Stanford University | 1981 |

| RISC | ARM | Arm Holdings, Apple, Qualcomm, Samsung, Renesas | 1985 |

| RISC | MIPS | MIPS Computer Systems, Inc, Loongson, Broadcom | 1986 |

| RISC | PowerPC | Apple–IBM–Motorola alliance, known as AIM, IBM | 1992 |

| RISC | Atmel AVR | Atmel Corporation | 1996 |

| RISC | RISC-V | RISC-V Foundation, StarFive, GigaDevice, T-Head | 2011 |

ISA: Instruction Set Architecture

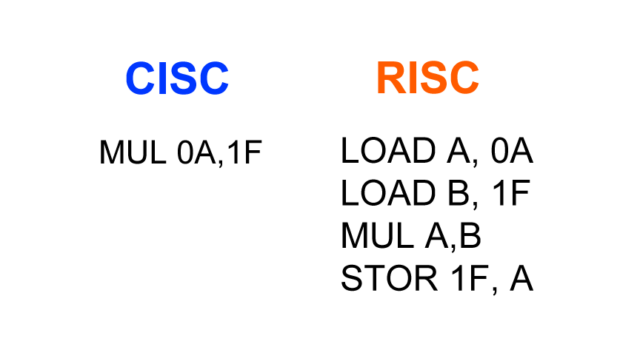

CISC: Complex instruction set computer

RISC: Reduced instruction set computer

MIPS: Microprocessor without Interlocked Pipeline Stages

ref: https://cloud.tencent.com/developer/article/1862717?areaId=106001

ref: https://en.wikipedia.org/wiki/IBM_System/360

ref: https://en.wikipedia.org/wiki/Intel_8080

ref: https://en.wikipedia.org/wiki/MOS_Technology_6502

ref: https://en.wikipedia.org/wiki/X86

ref: https://en.wikipedia.org/wiki/MIPS_Technologies

ref: https://en.wikipedia.org/wiki/PowerPC

ref: https://en.wikipedia.org/wiki/List_of_ARM_processors

ref: https://en.wikipedia.org/wiki/AVR_microcontrollers

ref: https://en.wikipedia.org/wiki/RISC-V

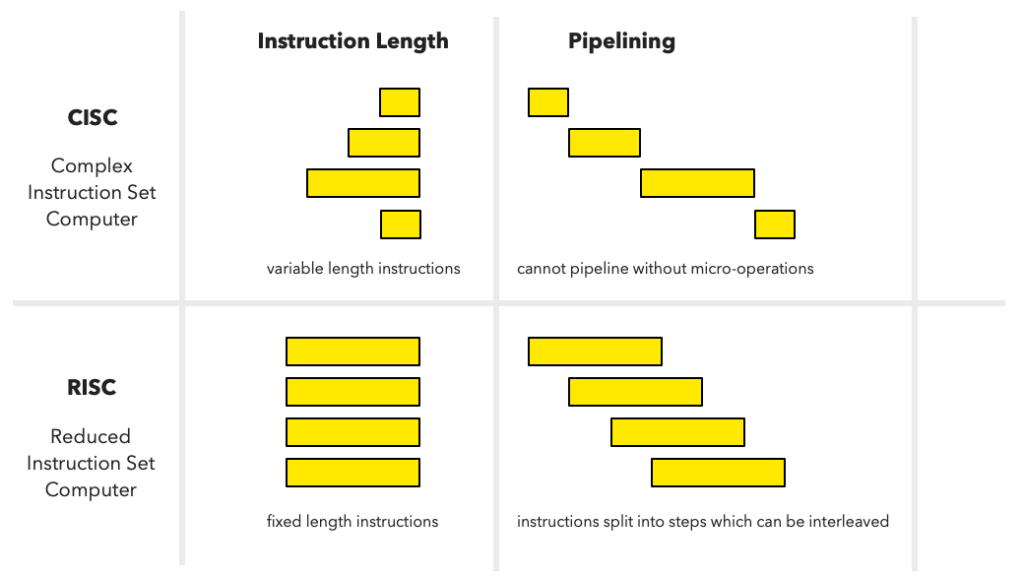

RISC Principles

The RISC philosophy is specifically targetted at high performance. Its fundamental principle is:

- Add complexity only to make common cases faster.

Corollaries

The fundamental principle has two important corollaries:

- Instruction operands should be simple.

- Instruction operations should be abstractly simple. If an operation can be broken down into a sequence of simpler instructions, it should only be added as an instruction if it improves overall performance.

Consequences

Observing the corollary principles usually results in the following consequences:

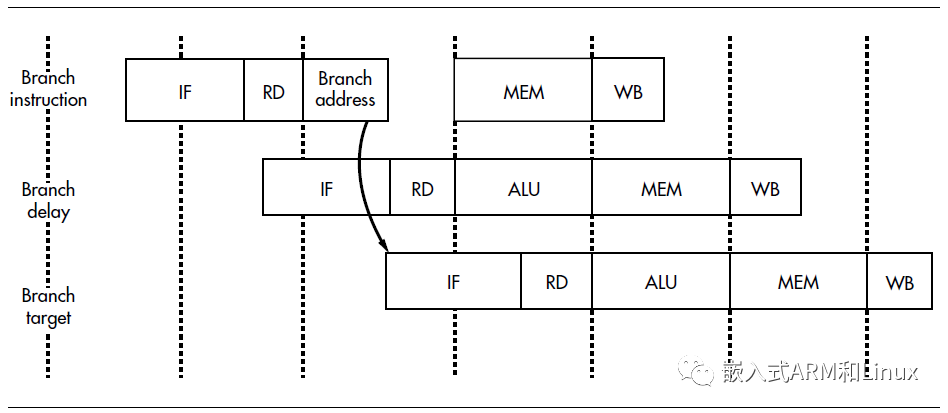

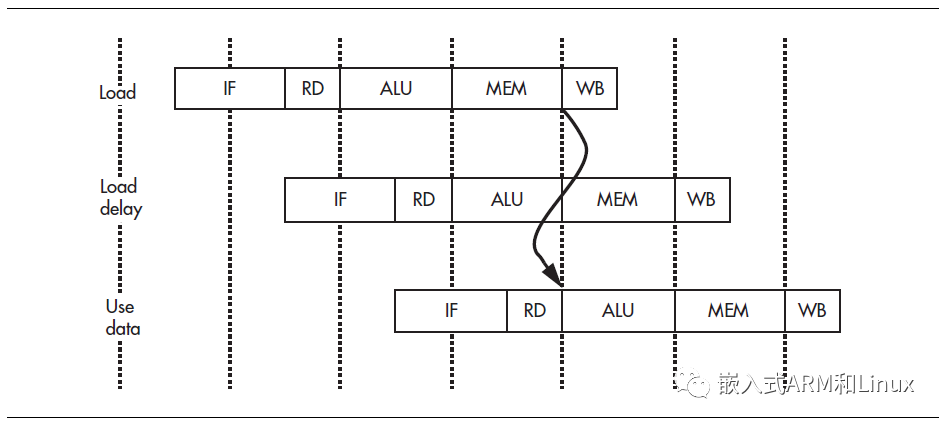

- Simple, fast control

- Fixed-length instructions

- Easier pipelining

- Easier handling of dependences between instructions

ref: https://www.d.umn.edu/~gshute/arch/risc-principles.html

ref: https://minnie.tuhs.org/CompArch/Lectures/week02.html

ref: https://en.wikipedia.org/wiki/Atmel_AVR_instruction_set

ref: https://itnext.io/risc-vs-cisc-microprocessor-philosophy-in-2022-fa871861bc94

ref: https://arstechnica.com/gadgets/2022/09/a-history-of-arm-part-1-building-the-first-chip/3/

ref: https://cloud.tencent.com/developer/article/2073027

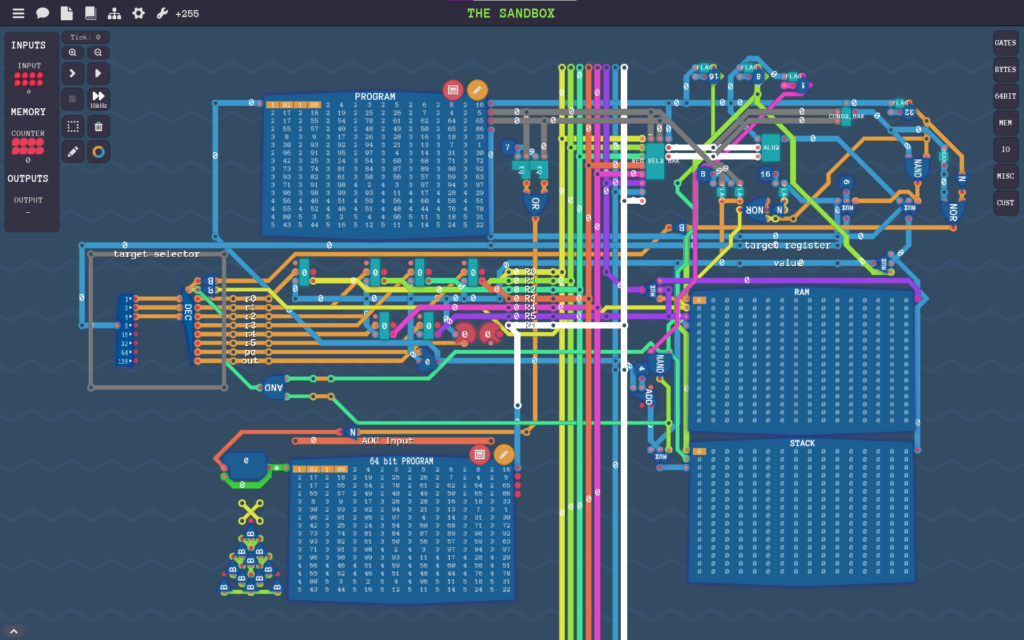

Turning complete

ref: https://goodcssm.live/product_details/54436859.html